# Section I. Cyclone FPGA Family Data Sheet

This section provides designers with the data sheet specifications for Cyclone devices. The chapters contain feature definitions of the internal architecture, configuration and JTAG boundary-scan testing information, DC operating conditions, AC timing parameters, a reference to power consumption, and ordering information for Cyclone devices.

This section contains the following chapters:

- Chapter 1. Introduction

- Chapter 2. Cyclone Architecture

- Chapter 3. Configuration & Testing

- Chapter 4. DC & Switching Characteristics

- Chapter 5. Reference & Ordering Information

# **Revision History** The table below shows the revision history for Chapters 1 through 5.

| Chapter(s) | Date / Version         | Changes Made                                                                               |

|------------|------------------------|--------------------------------------------------------------------------------------------|

| 1          | October 2003<br>v1.2   | Added 64-bit PCI support information.                                                      |

|            | September 2003<br>v1.1 | Updated LVDS data rates to 640 Mbps from<br>311 Mbps.<br>Updated RSDS feature information. |

|            | May 2003<br>v1.0       | Added document to Cyclone Device Handbook.                                                 |

| 2          | October 2003<br>v1.2   | Updated phase shift information.<br>Added 64-bit PCI support information.                  |

|            | September 2003<br>v1.1 | Updated LVDS data rates to 640 Mbps from 311 Mbps.                                         |

|            | May 2003<br>v1.0       | Added document to Cyclone Device Handbook.                                                 |

| 3          | May 2003<br>v1.0       | Added document to Cyclone Device Handbook.                                                 |

| Chapter(s) | Date / Version        | Changes Made                                                                                                                                                                                                                                        |

|------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4          | January 2004<br>v.1.3 | Added extended-temperature grade device<br>information. Updated Table 4–2.<br>Updated ICC0 information in Table 4–3.                                                                                                                                |

|            | October 2003<br>v.1.2 | Added clock tree information in Table 4–19.<br>Finalized timing information for EP1C3 and<br>EP1C12 devices. Updated timing information<br>inTables 4–25 through 4–26 and Tables 4–30<br>through 4–51.<br>Updated PLL specifications in Table 4–52. |

|            | July 2003<br>v1.1     | Updated timing information. Timing finalized for<br>EP1C6 and EP1C20 devices. Updated<br>performance information. Added "PLL Timing"<br>section.                                                                                                    |

|            | May 2003<br>v1.0      | Added document to Cyclone Device Handbook.                                                                                                                                                                                                          |

| 5          | May 2003<br>v1.0      | Added document to Cyclone Device Handbook.                                                                                                                                                                                                          |

# 1. Introduction

#### C51001-1.2

# Introduction

The Cyclone<sup>TM</sup> field programmable gate array family is based on a 1.5-V, 0.13-µm, all-layer copper SRAM process, with densities up to 20,060 logic elements (LEs) and up to 288 Kbits of RAM. With features like phase-locked loops (PLLs) for clocking and a dedicated double data rate (DDR) interface to meet DDR SDRAM and fast cycle RAM (FCRAM) memory requirements, Cyclone devices are a cost-effective solution for data-path applications. Cyclone devices support various I/O standards, including LVDS at data rates up to 640 megabits per second (Mbps), and 66- and 33-MHz, 64- and 32-bit peripheral component interconnect (PCI), for interfacing with and supporting ASSP and ASIC devices. Altera also offers new low-cost serial configuration devices to configure Cyclone devices.

The following shows the main sections in the Cyclone FPGA Family Data Sheet:

| Section                                                                                                                                                                                                        | Page                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| Features                                                                                                                                                                                                       | . 1–2                                          |

| Functional Description<br>Logic Array Blocks<br>Logic Elements<br>MultiTrack Interconnect<br>Embedded Memory<br>Global Clock Network & Phase-Locked Loops<br>I/O Structure<br>Power Sequencing & Hot Socketing | . 2–3<br>. 2–5<br>2–12<br>2–18<br>2–29<br>2–39 |

| IEEE Std. 1149.1 (JTAG) Boundary Scan Support.         SignalTap II Embedded Logic Analyzer         Configuration         Operating Conditions         Power Consumption         Timing Model                  | . 3–1<br>. 3–5<br>. 3–5<br>. 4–1<br>. 4–8      |

| Software.<br>Device Pin-Outs<br>Ordering Information                                                                                                                                                           | . 5–1                                          |

# Features

The Cyclone device family offers the following features:

- 2,910 to 20,060 LEs, see Table 1–1

- Up to 294,912 RAM bits (36,864 bytes)

- Supports configuration through low-cost serial configuration device

- Support for LVTTL, LVCMOS, SSTL-2, and SSTL-3 I/O standards

- Support for 66- and 33-MHz, 64- and 32-bit PCI standard

- High-speed (640 Mbps) LVDS I/O support

- Low-speed (311 Mbps) LVDS I/O support

- 311-Mbps RSDS I/O support

- Up to two PLLs per device provide clock multiplication and phase shifting

- Up to eight global clock lines with six clock resources available per logic array block (LAB) row

- Support for external memory, including DDR SDRAM (133 MHz), FCRAM, and single data rate (SDR) SDRAM

- Support for multiple intellectual property (IP) cores, including Altera® MegaCore® functions and Altera Megafunctions Partners Program (AMPP<sup>SM</sup>) megafunctions.

| Table 1–1. Cyclone Device Features    |        |        |        |         |         |  |  |

|---------------------------------------|--------|--------|--------|---------|---------|--|--|

| Feature                               | EP1C3  | EP1C4  | EP1C6  | EP1C12  | EP1C20  |  |  |

| LEs                                   | 2,910  | 4,000  | 5,980  | 12,060  | 20,060  |  |  |

| M4K RAM blocks (128 $\times$ 36 bits) | 13     | 17     | 20     | 52      | 64      |  |  |

| Total RAM bits                        | 59,904 | 78,336 | 92,160 | 239,616 | 294,912 |  |  |

| PLLs                                  | 1      | 2      | 2      | 2       | 2       |  |  |

| Maximum user I/O pins (1)             | 104    | 301    | 185    | 249     | 301     |  |  |

Note to Table 1–1:

(1) This parameter includes global clock pins.

Cyclone devices are available in quad flat pack (QFP) and space-saving FineLine BGA<sup>®</sup> packages (see Table 1–2 through 1–3).

| Table 1–2. Cyclone Package Options & I/O Pin Counts |                            |                                 |                            |                         |                         |                         |  |  |

|-----------------------------------------------------|----------------------------|---------------------------------|----------------------------|-------------------------|-------------------------|-------------------------|--|--|

| Device                                              | <b>100-Pin TQFP</b><br>(1) | <b>144-Pin TQFP</b><br>(1), (2) | <b>240-Pin PQFP</b><br>(1) | 256-Pin<br>FineLine BGA | 324-Pin<br>FineLine BGA | 400-Pin<br>FineLine BGA |  |  |

| EP1C3                                               | 65                         | 104                             |                            |                         |                         |                         |  |  |

| EP1C4                                               |                            |                                 |                            |                         | 249                     | 301                     |  |  |

| EP1C6                                               |                            | 98                              | 185                        | 185                     |                         |                         |  |  |

| EP1C12                                              |                            |                                 | 173                        | 185                     | 249                     |                         |  |  |

| EP1C20                                              |                            |                                 |                            |                         | 233                     | 301                     |  |  |

#### *Notes to Table 1–2:*

(1) TQFP: thin quad flat pack.

PQFP: plastic quad flat pack.

(2) Cyclone devices support vertical migration within the same package (i.e., designers can migrate between the EP1C3 device in the 144-pin TQFP package and the EP1C6 device in the same package)

| Table 1–3. Cyclone QFP & FineLine BGA Package Sizes |                 |                 |                 |                            |                            |                            |  |

|-----------------------------------------------------|-----------------|-----------------|-----------------|----------------------------|----------------------------|----------------------------|--|

| Dimension                                           | 100-Pin<br>TQFP | 144-Pin<br>TQFP | 240-Pin<br>PQFP | 256-Pin<br>FineLine<br>BGA | 324-Pin<br>FineLine<br>BGA | 400-Pin<br>FineLine<br>BGA |  |

| Pitch (mm)                                          | 0.5             | 0.5             | 0.5             | 1.0                        | 1.0                        | 1.0                        |  |

| Area (mm <sup>2</sup> )                             | 256             | 484             | 1,024           | 289                        | 361                        | 441                        |  |

| Length $\times$ width (mm $\times$ mm)              | 16 × 16         | 22 × 22         | 34.6 × 34.6     | 17 × 17                    | 19 × 19                    | 21 × 21                    |  |

# 2. Cyclone Architecture

C51002-1.2

# Functional Description

Cyclone devices contain a two-dimensional row- and column-based architecture to implement custom logic. Column and row interconnects of varying speeds provide signal interconnects between LABs and embedded memory blocks.

The logic array consists of LABs, with 10 LEs in each LAB. An LE is a small unit of logic providing efficient implementation of user logic functions. LABs are grouped into rows and columns across the device. Cyclone devices range between 2,910 to 20,060 LEs.

M4K RAM blocks are true dual-port memory blocks with 4K bits of memory plus parity (4,608 bits). These blocks provide dedicated true dual-port, simple dual-port, or single-port memory up to 36-bits wide at up to 200 MHz. These blocks are grouped into columns across the device in between certain LABs. Cyclone devices offer between 60 to 288 Kbits of embedded RAM.

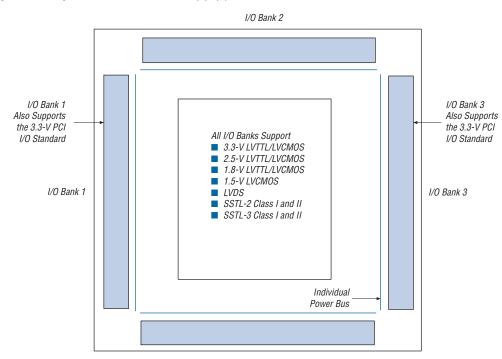

Each Cyclone device I/O pin is fed by an I/O element (IOE) located at the ends of LAB rows and columns around the periphery of the device. I/O pins support various single-ended and differential I/O standards, such as the 66- and 33-MHz, 64- and 32-bit PCI standard and the LVDS I/O standard at up to 640 Mbps. Each IOE contains a bidirectional I/O buffer and three registers for registering input, output, and output-enable signals. Dual-purpose DQS, DQ, and DM pins along with delay chains (used to phase-align DDR signals) provide interface support with external memory devices such as DDR SDRAM, and FCRAM devices at up to 133 MHz (266 Mbps).

Cyclone devices provide a global clock network and up to two PLLs. The global clock network consists of eight global clock lines that drive throughout the entire device. The global clock network can provide clocks for all resources within the device, such as IOEs, LEs, and memory blocks. The global clock lines can also be used for control signals. Cyclone PLLs provide general-purpose clocking with clock multiplication and phase shifting as well as external outputs for high-speed differential I/O support.

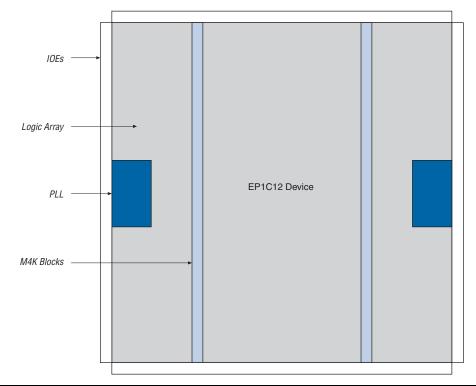

Figure 2–1 shows a diagram of the Cyclone EP1C12 device.

Figure 2–1. Cyclone EP1C12 Device Block Diagram

The number of M4K RAM blocks, PLLs, rows, and columns vary per device. Table 2–1 lists the resources available in each Cyclone device.

| Table 2–1. Cyclone Device Resources |         |        |      |               |          |  |  |

|-------------------------------------|---------|--------|------|---------------|----------|--|--|

| Daviaa                              | M4K     | RAM    | PLLs | LAB Columns   |          |  |  |

| Device                              | Columns | Blocks | FLLS | LAD CUIUIIIIS | LAB Rows |  |  |

| EP1C3                               | 1       | 13     | 1    | 24            | 13       |  |  |

| EP1C4                               | 1       | 17     | 2    | 26            | 17       |  |  |

| EP1C6                               | 1       | 20     | 2    | 32            | 20       |  |  |

| EP1C12                              | 2       | 52     | 2    | 48            | 26       |  |  |

| EP1C20                              | 2       | 64     | 2    | 64            | 32       |  |  |

# **Logic Array** Blocks

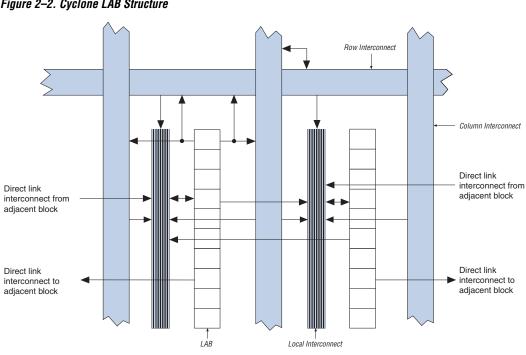

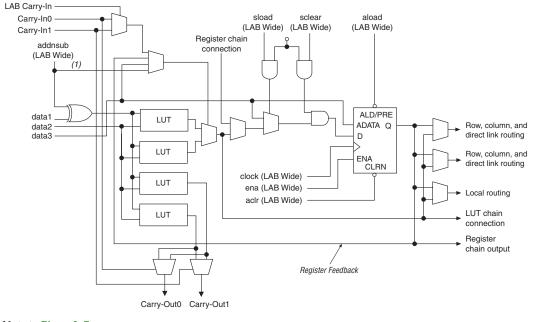

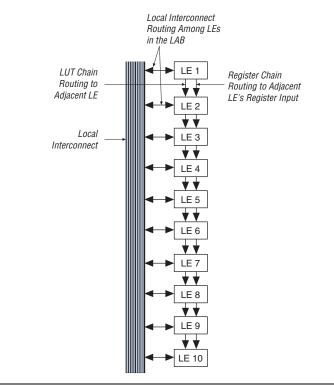

Each LAB consists of 10 LEs, LE carry chains, LAB control signals, a local interconnect, look-up table (LUT) chain, and register chain connection lines. The local interconnect transfers signals between LEs in the same LAB. LUT chain connections transfer the output of one LE's LUT to the adjacent LE for fast sequential LUT connections within the same LAB. Register chain connections transfer the output of one LE's register to the adjacent LE's register within an LAB. The Quartus® II Compiler places associated logic within an LAB or adjacent LABs, allowing the use of local, LUT chain, and register chain connections for performance and area efficiency. Figure 2-2 details the Cyclone LAB.

#### Figure 2–2. Cyclone LAB Structure

## LAB Interconnects

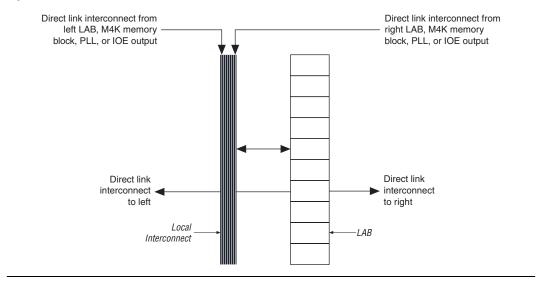

The LAB local interconnect can drive LEs within the same LAB. The LAB local interconnect is driven by column and row interconnects and LE outputs within the same LAB. Neighboring LABs, PLLs, and M4K RAM blocks from the left and right can also drive an LAB's local interconnect through the direct link connection. The direct link connection feature minimizes the use of row and column interconnects, providing higher

performance and flexibility. Each LE can drive 30 other LEs through fast local and direct link interconnects. Figure 2–3 shows the direct link connection.

#### Figure 2–3. Direct Link Connection

### **LAB Control Signals**

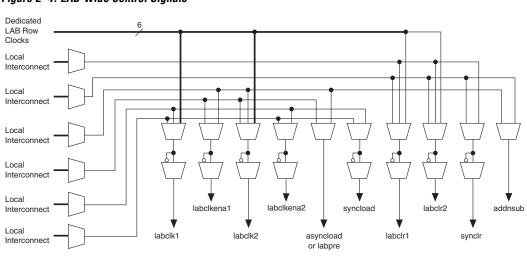

Each LAB contains dedicated logic for driving control signals to its LEs. The control signals include two clocks, two clock enables, two asynchronous clears, synchronous clear, asynchronous preset/load, synchronous load, and add/subtract control signals. This gives a maximum of 10 control signals at a time. Although synchronous load and clear signals are generally used when implementing counters, they can also be used with other functions.

Each LAB can use two clocks and two clock enable signals. Each LAB's clock and clock enable signals are linked. For example, any LE in a particular LAB using the labclk1 signal will also use labclkena1. If the LAB uses both the rising and falling edges of a clock, it also uses both LAB-wide clock signals. De-asserting the clock enable signal will turn off the LAB-wide clock.

Each LAB can use two asynchronous clear signals and an asynchronous load/preset signal. The asynchronous load acts as a preset when the asynchronous load data input is tied high.

With the LAB-wide addnsub control signal, a single LE can implement a one-bit adder and subtractor. This saves LE resources and improves performance for logic functions such as DSP correlators and signed multipliers that alternate between addition and subtraction depending on data.

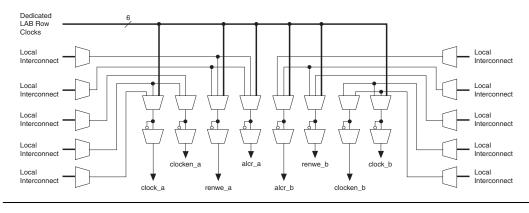

The LAB row clocks [5..0] and LAB local interconnect generate the LABwide control signals. The MultiTrack<sup>TM</sup> interconnect's inherent low skew allows clock and control signal distribution in addition to data. Figure 2–4 shows the LAB control signal generation circuit.

Figure 2–4. LAB-Wide Control Signals

# **Logic Elements**

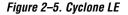

The smallest unit of logic in the Cyclone architecture, the LE, is compact and provides advanced features with efficient logic utilization. Each LE contains a four-input LUT, which is a function generator that can implement any function of four variables. In addition, each LE contains a programmable register and carry chain with carry select capability. A single LE also supports dynamic single bit addition or subtraction mode selectable by an LAB-wide control signal. Each LE drives all types of interconnects: local, row, column, LUT chain, register chain, and direct link interconnects. See Figure 2–5.

Each LE's programmable register can be configured for D, T, JK, or SR operation. Each register has data, true asynchronous load data, clock, clock enable, clear, and asynchronous load/preset inputs. Global signals, general-purpose I/O pins, or any internal logic can drive the register's clock and clear control signals. Either general-purpose I/O pins or internal logic can drive the clock enable, preset, asynchronous load, and asynchronous data. The asynchronous load data input comes from the data3 input of the LE. For combinatorial functions, the LUT output bypasses the register and drives directly to the LE outputs.

Each LE has three outputs that drive the local, row, and column routing resources. The LUT or register output can drive these three outputs independently. Two LE outputs drive column or row and direct link routing connections and one drives local interconnect resources. This allows the LUT to drive one output while the register drives another output. This feature, called register packing, improves device utilization because the device can use the register and the LUT for unrelated

functions. Another special packing mode allows the register output to feed back into the LUT of the same LE so that the register is packed with its own fan-out LUT. This provides another mechanism for improved fitting. The LE can also drive out registered and unregistered versions of the LUT output.

# LUT Chain & Register Chain

In addition to the three general routing outputs, the LEs within an LAB have LUT chain and register chain outputs. LUT chain connections allow LUTs within the same LAB to cascade together for wide input functions. Register chain outputs allow registers within the same LAB to cascade together. The register chain output allows an LAB to use LUTs for a single combinatorial function and the registers to be used for an unrelated shift register implementation. These resources speed up connections between LABs while saving local interconnect resources. "MultiTrack Interconnect" on page 2–12 for more information on LUT chain and register chain connections.

# addnsub Signal

The LE's dynamic adder/subtractor feature saves logic resources by using one set of LEs to implement both an adder and a subtractor. This feature is controlled by the LAB-wide control signal addnsub. The addnsub signal sets the LAB to perform either A + B or A - B. The LUT computes addition; subtraction is computed by adding the two's complement of the intended subtractor. The LAB-wide signal converts to two's complement by inverting the B bits within the LAB and setting carry-in = 1 to add one to the least significant bit (LSB). The LSB of an adder/subtractor must be placed in the first LE of the LAB, where the LAB-wide addnsub signal automatically sets the carry-in to 1. The Quartus II Compiler automatically places and uses the adder/subtractor feature when using adder/subtractor parameterized functions.

# **LE Operating Modes**

The Cyclone LE can operate in one of the following modes:

- Normal mode

- Dynamic arithmetic mode

Each mode uses LE resources differently. In each mode, eight available inputs to the LE—the four data inputs from the LAB local interconnect, carry-in0 and carry-in1 from the previous LE, the LAB carry-in from the previous carry-chain LAB, and the register chain connection—are directed to different destinations to implement the desired logic function. LAB-wide signals provide clock, asynchronous

clear, asynchronous preset/load, synchronous clear, synchronous load, and clock enable control for the register. These LAB-wide signals are available in all LE modes. The addnsub control signal is allowed in arithmetic mode.

The Quartus II software, in conjunction with parameterized functions such as library of parameterized modules (LPM) functions, automatically chooses the appropriate mode for common functions such as counters, adders, subtractors, and arithmetic functions. If required, the designer can also create special-purpose functions that specify which LE operating mode to use for optimal performance.

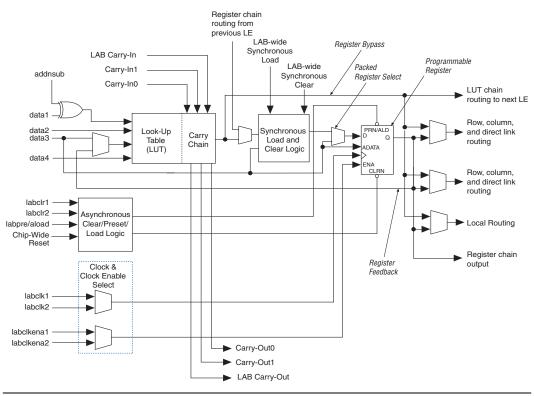

### Normal Mode

The normal mode is suitable for general logic applications and combinatorial functions. In normal mode, four data inputs from the LAB local interconnect are inputs to a four-input LUT (see Figure 2–6). The Quartus II Compiler automatically selects the carry-in or the data3 signal as one of the inputs to the LUT. Each LE can use LUT chain connections to drive its combinatorial output directly to the next LE in the LAB. Asynchronous load data for the register comes from the data3 input of the LE. LEs in normal mode support packed registers.

#### Note to Figure 2-6:

(1) This signal is only allowed in normal mode if the LE is at the end of an adder/subtractor chain.

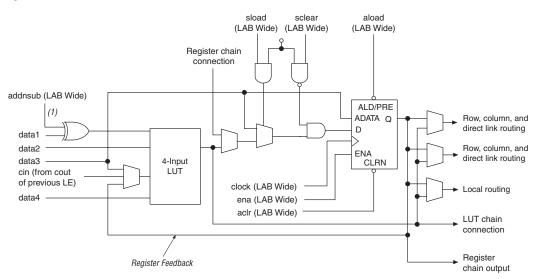

### Dynamic Arithmetic Mode

The dynamic arithmetic mode is ideal for implementing adders, counters, accumulators, wide parity functions, and comparators. An LE in dynamic arithmetic mode uses four 2-input LUTs configurable as a dynamic adder/subtractor. The first two 2-input LUTs compute two summations based on a possible carry-in of 1 or 0; the other two LUTs generate carry outputs for the two chains of the carry select circuitry. As shown in Figure 2–7, the LAB carry-in signal selects either the carry-in0 or carry-in1 chain. The selected chain's logic level in turn determines which parallel sum is generated as a combinatorial or registered output. For example, when implementing an adder, the sum output is the selection of two possible calculated sums:

data1 + data2 + carry-in0

or

data1 + data2 + carry-in1

The other two LUTs use the data1 and data2 signals to generate two possible carry-out signals—one for a carry of 1 and the other for a carry of 0. The carry-in0 signal acts as the carry select for the carry-out0 output and carry-in1 acts as the carry select for the carry-out1 output. LEs in arithmetic mode can drive out registered and unregistered versions of the LUT output.

The dynamic arithmetic mode also offers clock enable, counter enable, synchronous up/down control, synchronous clear, synchronous load, and dynamic adder/subtractor options. The LAB local interconnect data inputs generate the counter enable and synchronous up/down control signals. The synchronous clear and synchronous load options are LAB-wide signals that affect all registers in the LAB. The Quartus II software automatically places any registers that are not used by the counter into other LABs. The addnsub LAB-wide signal controls whether the LE acts as an adder or subtractor.

Figure 2–7. LE in Dynamic Arithmetic Mode

Note to Figure 2–7:

(1) The addnsub signal is tied to the carry input for the first LE of a carry chain only.

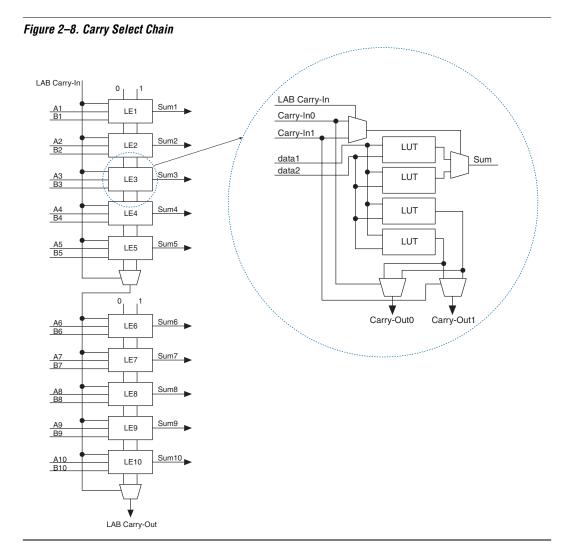

### Carry-Select Chain

The carry-select chain provides a very fast carry-select function between LEs in dynamic arithmetic mode. The carry-select chain uses the redundant carry calculation to increase the speed of carry functions. The LE is configured to calculate outputs for a possible carry-in of 0 and carry-in of 1 in parallel. The carry-in0 and carry-in1 signals from a lower-order bit feed forward into the higher-order bit via the parallel carry chain and feed into both the LUT and the next portion of the carry chain. Carry-select chains can begin in any LE within an LAB.

The speed advantage of the carry-select chain is in the parallel precomputation of carry chains. Since the LAB carry-in selects the precomputed carry chain, not every LE is in the critical path. Only the propagation delays between LAB carry-in generation (LE 5 and LE 10) are now part of the critical path. This feature allows the Cyclone architecture to implement high-speed counters, adders, multipliers, parity functions, and comparators of arbitrary width. Figure 2–8 shows the carry-select circuitry in an LAB for a 10-bit full adder. One portion of the LUT generates the sum of two bits using the input signals and the appropriate carry-in bit; the sum is routed to the output of the LE. The register can be bypassed for simple adders or used for accumulator functions. Another portion of the LUT generates carry-out bits. An LAB-wide carry-in bit selects which chain is used for the addition of given inputs. The carry-in signal for each chain, carry-in0 or carry-in1, selects the carry-out to carry forward to the carry-in signal of the next-higher-order bit. The final carry-out signal is routed to an LE, where it is fed to local, row, or column interconnects.

Altera Corporation October 2003 The Quartus II Compiler automatically creates carry chain logic during design processing, or the designer can create it manually during design entry. Parameterized functions such as LPM functions automatically take advantage of carry chains for the appropriate functions.

The Quartus II Compiler creates carry chains longer than 10 LEs by linking LABs together automatically. For enhanced fitting, a long carry chain runs vertically allowing fast horizontal connections to M4K memory blocks. A carry chain can continue as far as a full column.

### Clear & Preset Logic Control

LAB-wide signals control the logic for the register's clear and preset signals. The LE directly supports an asynchronous clear and preset function. The register preset is achieved through the asynchronous load of a logic high. The direct asynchronous preset does not require a NOTgate push-back technique. Cyclone devices support simultaneous preset/ asynchronous load and clear signals. An asynchronous clear signal takes precedence if both signals are asserted simultaneously. Each LAB supports up to two clears and one preset signal.

In addition to the clear and preset ports, Cyclone devices provide a chipwide reset pin (DEV\_CLRn) that resets all registers in the device. An option set before compilation in the Quartus II software controls this pin. This chip-wide reset overrides all other control signals.

# MultiTrack Interconnect

In the Cyclone architecture, connections between LEs, M4K memory blocks, and device I/O pins are provided by the MultiTrack interconnect structure with DirectDrive<sup>TM</sup> technology. The MultiTrack interconnect consists of continuous, performance-optimized routing lines of different speeds used for inter- and intra-design block connectivity. The Quartus II Compiler automatically places critical design paths on faster interconnects to improve design performance.

DirectDrive technology is a deterministic routing technology that ensures identical routing resource usage for any function regardless of placement within the device. The MultiTrack interconnect and DirectDrive technology simplify the integration stage of block-based designing by eliminating the re-optimization cycles that typically follow design changes and additions.

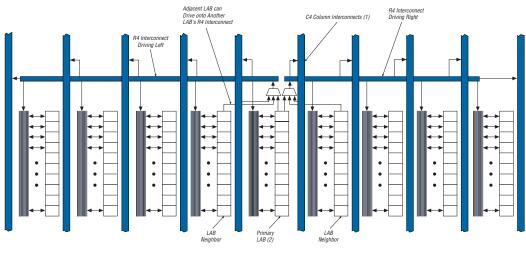

The MultiTrack interconnect consists of row and column interconnects that span fixed distances. A routing structure with fixed length resources for all devices allows predictable and repeatable performance when migrating through different device densities. Dedicated row interconnects route signals to and from LABs, PLLs, and M4K memory blocks within the same row. These row resources include:

- Direct link interconnects between LABs and adjacent blocks

- R4 interconnects traversing four blocks to the right or left

The direct link interconnect allows an LAB or M4K memory block to drive into the local interconnect of its left and right neighbors. Only one side of a PLL block interfaces with direct link and row interconnects. The direct link interconnect provides fast communication between adjacent LABs and/or blocks without using row interconnect resources.

The R4 interconnects span four LABs, or two LABs and one M4K RAM block. These resources are used for fast row connections in a four-LAB region. Every LAB has its own set of R4 interconnects to drive either left or right. Figure 2–9 shows R4 interconnect connections from an LAB. R4 interconnects can drive and be driven by M4K memory blocks, PLLs, and row IOEs. For LAB interfacing, a primary LAB or LAB neighbor can drive a given R4 interconnect. For R4 interconnects that drive to the right, the primary LAB and right neighbor can drive on to the interconnect. For R4 interconnects can drive on to the interconnect. For R4 interconnects can drive other R4 interconnects to extend the range of LABs they can drive. R4 interconnects can also drive C4 interconnects for connections from one row to another.

#### Notes to Figure 2–9:

- (1) C4 interconnects can drive R4 interconnects.

- (2) This pattern is repeated for every LAB in the LAB row.

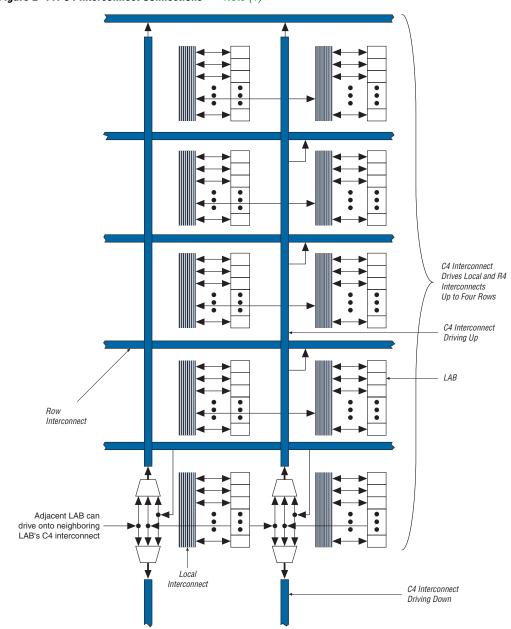

The column interconnect operates similarly to the row interconnect. Each column of LABs is served by a dedicated column interconnect, which vertically routes signals to and from LABs, M4K memory blocks, and row and column IOEs. These column resources include:

- LUT chain interconnects within an LAB

- Register chain interconnects within an LAB

- C4 interconnects traversing a distance of four blocks in an up and down direction

Cyclone devices include an enhanced interconnect structure within LABs for routing LE output to LE input connections faster using LUT chain connections and register chain connections. The LUT chain connection allows the combinatorial output of an LE to directly drive the fast input of the LE right below it, bypassing the local interconnect. These resources can be used as a high-speed connection for wide fan-in functions from LE 1 to LE 10 in the same LAB. The register chain connection allows the register output of one LE to connect directly to the register input of the next LE in the LAB for fast shift registers. The Quartus II Compiler automatically takes advantage of these resources to improve utilization and performance. Figure 2–10 shows the LUT chain and register chain interconnects.

Figure 2–10. LUT Chain & Register Chain Interconnects

The C4 interconnects span four LABs or M4K blocks up or down from a source LAB. Every LAB has its own set of C4 interconnects to drive either up or down. Figure 2–11 shows the C4 interconnect connections from an LAB in a column. The C4 interconnects can drive and be driven by all types of architecture blocks, including PLLs, M4K memory blocks, and column and row IOEs. For LAB interconnection, a primary LAB or its LAB neighbor can drive a given C4 interconnect. C4 interconnects can drive each other to extend their range as well as drive row interconnects for column-to-column connections.

Figure 2–11. C4 Interconnect Connections Note (1)

(1) Each C4 interconnect can drive either up or down four rows.

All embedded blocks communicate with the logic array similar to LABto-LAB interfaces. Each block (i.e., M4K memory or PLL) connects to row and column interconnects and has local interconnect regions driven by row and column interconnects. These blocks also have direct link interconnects for fast connections to and from a neighboring LAB.

Table 2–2 shows the Cyclone device's routing scheme.

| Table 2–2. Cyclone Device Routing Scheme |              |                |                    |                          |                 |                 |              |               |              |              |              |

|------------------------------------------|--------------|----------------|--------------------|--------------------------|-----------------|-----------------|--------------|---------------|--------------|--------------|--------------|

|                                          |              | Destination    |                    |                          |                 |                 |              |               |              |              |              |

| Source                                   | LUT Chain    | Register Chain | Local Interconnect | Direct Link Interconnect | R4 Interconnect | C4 Interconnect | T            | M4K RAM Block | PLL          | Column 10E   | Row IDE      |

| LUT Chain                                |              |                |                    |                          |                 |                 | $\checkmark$ |               |              |              |              |

| Register Chain                           |              |                |                    |                          |                 |                 | $\checkmark$ |               |              |              |              |

| Local Interconnect                       |              |                |                    |                          |                 |                 | $\checkmark$ | $\checkmark$  | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Direct Link<br>Interconnect              |              |                | ~                  |                          |                 |                 |              |               |              |              |              |

| R4 Interconnect                          |              |                | $\checkmark$       |                          | $\checkmark$    | $\checkmark$    |              |               |              |              |              |

| C4 Interconnect                          |              |                | $\checkmark$       |                          | $\checkmark$    | $\checkmark$    |              |               |              |              |              |

| LE                                       | $\checkmark$ | $\checkmark$   | $\checkmark$       | $\checkmark$             | $\checkmark$    | $\checkmark$    |              |               |              |              |              |

| M4K RAM Block                            |              |                | $\checkmark$       | $\checkmark$             | $\checkmark$    | $\checkmark$    |              |               |              |              |              |

| PLL                                      |              |                |                    | $\checkmark$             | $\checkmark$    | $\checkmark$    |              |               |              |              |              |

| Column IOE                               |              |                |                    |                          |                 | $\checkmark$    |              |               |              |              |              |

| Row IOE                                  |              |                |                    | $\checkmark$             | $\checkmark$    | $\checkmark$    |              |               |              |              |              |

# Embedded Memory

The Cyclone embedded memory consists of columns of M4K memory blocks. EP1C3 and EP1C6 devices have one column of M4K blocks, while EP1C12 and EP1C20 devices have two columns (see Table 1–1 on page 1–2 for total RAM bits per density). Each M4K block can implement various types of memory with or without parity, including true dual-port, simple dual-port, and single-port RAM, ROM, and FIFO buffers. The M4K blocks support the following features:

- 4,608 RAM bits

- 200 MHz performance

- True dual-port memory

- Simple dual-port memory

- Single-port memory

- Byte enable

- Parity bits

- Shift register

- FIFO buffer

- ROM

- Mixed clock mode

### **Memory Modes**

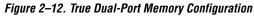

The M4K memory blocks include input registers that synchronize writes and output registers to pipeline designs and improve system performance. M4K blocks offer a true dual-port mode to support any combination of two-port operations: two reads, two writes, or one read and one write at two different clock frequencies. Figure 2–12 shows true dual-port memory.

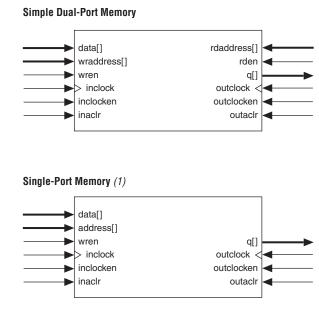

In addition to true dual-port memory, the M4K memory blocks support simple dual-port and single-port RAM. Simple dual-port memory supports a simultaneous read and write. Single-port memory supports non-simultaneous reads and writes. Figure 2–13 shows these different M4K RAM memory port configurations.

Figure 2–13. Simple Dual-Port & Single-Port Memory Configurations

#### Note to Figure 2–13:

Two single-port memory blocks can be implemented in a single M4K block as long as each of the two independent block sizes is equal to or less than half of the M4K block size.

The memory blocks also enable mixed-width data ports for reading and writing to the RAM ports in dual-port RAM configuration. For example, the memory block can be written in ×1 mode at port A and read out in ×16 mode from port B.

The Cyclone memory architecture can implement fully synchronous RAM by registering both the input and output signals to the M4K RAM block. All M4K memory block inputs are registered, providing synchronous write cycles. In synchronous operation, the memory block generates its own self-timed strobe write enable (wren) signal derived from a global clock. In contrast, a circuit using asynchronous RAM must generate the RAM wren signal while ensuring its data and address signals meet setup and hold time specifications relative to the wren signal. The output registers can be bypassed. Pseudo-asynchronous reading is possible in the simple dual-port mode of M4K blocks by clocking the read enable and read address registers on the negative clock edge and bypassing the output registers. When configured as RAM or ROM, the designer can use an initialization file to pre-load the memory contents.

Two single-port memory blocks can be implemented in a single M4K block as long as each of the two independent block sizes is equal to or less than half of the M4K block size.

The Quartus II software automatically implements larger memory by combining multiple M4K memory blocks. For example, two 256×16-bit RAM blocks can be combined to form a 256×32-bit RAM block. Memory performance does not degrade for memory blocks using the maximum number of words allowed. Logical memory blocks using less than the maximum number of words use physical blocks in parallel, eliminating any external control logic that would increase delays. To create a larger high-speed memory block, the Quartus II software automatically combines memory blocks with LE control logic.

# **Parity Bit Support**

The M4K blocks support a parity bit for each byte. The parity bit, along with internal LE logic, can implement parity checking for error detection to ensure data integrity. Designers can also use parity-size data words to store user-specified control bits. Byte enables are also available for data input masking during write operations.

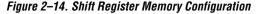

### Shift Register Support

The designer can configure M4K memory blocks to implement shift registers for DSP applications such as pseudo-random number generators, multi-channel filtering, auto-correlation, and crosscorrelation functions. These and other DSP applications require local data storage, traditionally implemented with standard flip-flops, which can quickly consume many logic cells and routing resources for large shift registers. A more efficient alternative is to use embedded memory as a shift register block, which saves logic cell and routing resources and provides a more efficient implementation with the dedicated circuitry.

The size of a  $w \times m \times n$  shift register is determined by the input data width (*w*), the length of the taps (*m*), and the number of taps (*n*). The size of a  $w \times m \times n$  shift register must be less than or equal to the maximum number of memory bits in the M4K block (4,608 bits). The total number of shift register outputs (number of taps  $n \times width w$ ) must be less than the maximum data width of the M4K RAM block (×36). To create larger shift registers, multiple memory blocks are cascaded together.

Data is written into each address location at the falling edge of the clock and read from the address at the rising edge of the clock. The shift register mode logic automatically controls the positive and negative edge clocking to shift the data in one clock cycle. Figure 2–14 shows the M4K memory block in the shift register mode.

### **Memory Configuration Sizes**

The memory address depths and output widths can be configured as  $4,096 \times 1, 2,048 \times 2, 1,024 \times 4, 512 \times 8$  (or  $512 \times 9$  bits),  $256 \times 16$  (or  $256 \times 18$  bits), and  $128 \times 32$  (or  $128 \times 36$  bits). The  $128 \times 32$ - or 36-bit configuration

is not available in the true dual-port mode. Mixed-width configurations are also possible, allowing different read and write widths. Tables 2–3 and 2–4 summarize the possible M4K RAM block configurations.

| Dood Dout |                      | Write Port   |               |              |              |              |              |          |              |

|-----------|----------------------|--------------|---------------|--------------|--------------|--------------|--------------|----------|--------------|

| Read Port | <b>4K</b> × <b>1</b> | 2K × 2       | $1K \times 4$ | 512 × 8      | 256 × 16     | 128 × 32     | 512 × 9      | 256 × 18 | 128 × 36     |

| 4K × 1    | $\checkmark$         | $\checkmark$ | $\checkmark$  | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |          |              |

| 2K × 2    | ~                    | $\checkmark$ | $\checkmark$  | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |          |              |

| 1K × 4    | $\checkmark$         | $\checkmark$ | $\checkmark$  | ~            | $\checkmark$ | $\checkmark$ |              |          |              |

| 512 × 8   | ~                    | $\checkmark$ | $\checkmark$  | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |          |              |

| 256 × 16  | $\checkmark$         | $\checkmark$ | $\checkmark$  | ~            | $\checkmark$ | $\checkmark$ |              |          |              |

| 128 × 32  | ~                    | $\checkmark$ | $\checkmark$  | ~            | $\checkmark$ | $\checkmark$ |              |          |              |

| 512 × 9   |                      |              |               |              |              |              | $\checkmark$ | ~        | ~            |

| 256 × 18  |                      |              |               |              |              |              | ~            | ~        | $\checkmark$ |

| 128 × 36  |                      |              |               |              |              |              | $\checkmark$ | ~        | $\checkmark$ |

| Table 2–4. M4K RAM Block Configurations (True Dual-Port) |              |              |              |              |              |             |          |

|----------------------------------------------------------|--------------|--------------|--------------|--------------|--------------|-------------|----------|

| Port A                                                   |              |              |              | Port B       |              |             |          |

| FUILA                                                    | 4K × 1       | 2K × 2       | 1K × 4       | 512 × 8      | 256 × 16     | 512 × 9     | 256 × 18 |

| 4K × 1                                                   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |             |          |

| 2K × 2                                                   | ~            | ~            | $\checkmark$ | $\checkmark$ | ~            |             |          |

| 1K × 4                                                   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | ~            |             |          |

| 512 × 8                                                  | ~            | ~            | ~            | ~            | ~            |             |          |

| 256 × 16                                                 | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | ~            |             |          |

| 512 × 9                                                  |              |              |              |              |              | <b>&gt;</b> | ~        |

| 256 × 18                                                 |              |              |              |              |              | ~           | ~        |

When the M4K RAM block is configured as a shift register block, the designer can create a shift register up to 4,608 bits ( $w \times m \times n$ ).

### Byte Enables

M4K blocks support byte writes when the write port has a data width of 16, 18, 32, or 36 bits. The byte enables allow the input data to be masked so the device can write to specific bytes. The unwritten bytes retain the previous written value. Table 2–5 summarizes the byte selection.

| Table 2–5. Byte Enable for M4K Blocks       Notes (1), (2) |             |             |  |  |  |  |

|------------------------------------------------------------|-------------|-------------|--|--|--|--|

| byteena[30]                                                | datain × 18 | datain × 36 |  |  |  |  |

| [0] = 1                                                    | [80]        | [80]        |  |  |  |  |

| [1] = 1                                                    | [179]       | [179]       |  |  |  |  |

| [2] = 1                                                    | -           | [2618]      |  |  |  |  |

| [3] = 1                                                    | -           | [3527]      |  |  |  |  |

#### Notes to Table 2–5:

(1) Any combination of byte enables is possible.

(2) Byte enables can be used in the same manner with 8-bit words, i.e., in ×16 and ×32 modes.

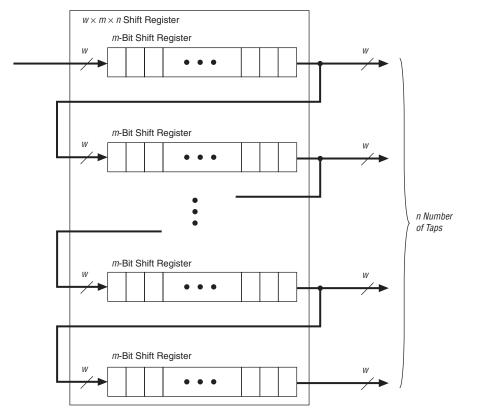

### Control Signals & M4K Interface

The M4K blocks allow for different clocks on their inputs and outputs. Either of the two clocks feeding the block can clock M4K block registers (renwe, address, byte enable, datain, and output registers). Only the output register can be bypassed. The six labclk signals or local interconnects can drive the control signals for the A and B ports of the M4K block. LEs can also control the clock\_a, clock\_b, renwe\_a, renwe\_b, clr\_a, clr\_b, clocken\_a, and clocken\_b signals, as shown in Figure 2–15.

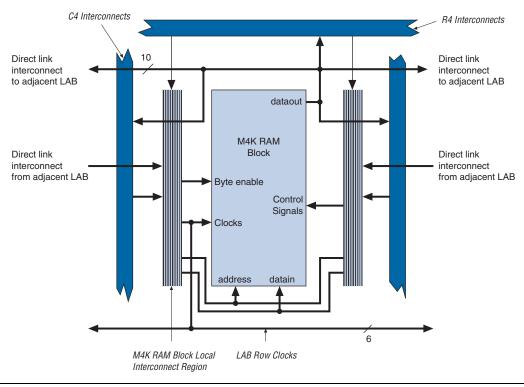

The R4, C4, and direct link interconnects from adjacent LABs drive the M4K block local interconnect. The M4K blocks can communicate with LABs on either the left or right side through these row resources or with LAB columns on either the right or left with the column resources. Up to 10 direct link input connections to the M4K block are possible from the left adjacent LABs and another 10 possible from the right adjacent LAB. M4K block outputs can also connect to left and right LABs through 10 direct link interconnects each. Figure 2–16 shows the M4K block to logic array interface.

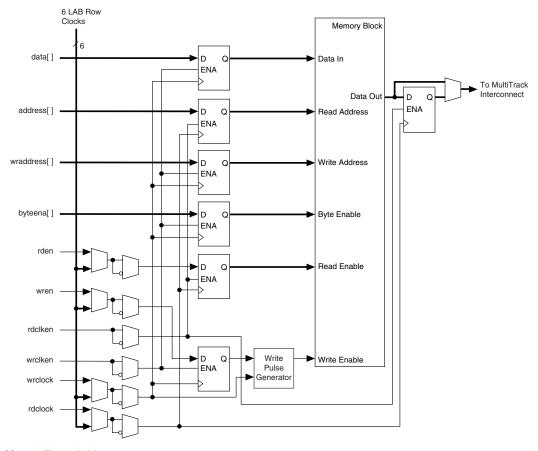

Figure 2–15. M4K RAM Block Control Signals

Figure 2–16. M4K RAM Block LAB Row Interface

# **Independent Clock Mode**

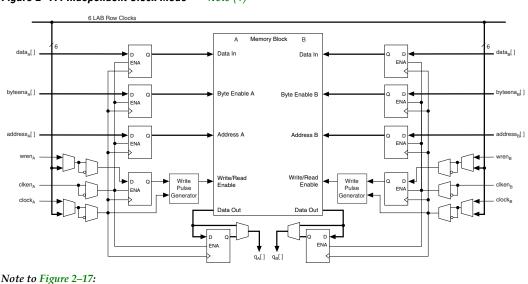

The M4K memory blocks implement independent clock mode for true dual-port memory. In this mode, a separate clock is available for each port (ports A and B). Clock A controls all registers on the port A side, while clock B controls all registers on the port B side. Each port, A and B, also supports independent clock enables and asynchronous clear signals for port A and B registers. Figure 2–17 shows an M4K memory block in independent clock mode.

Figure 2–17. Independent Clock Mode Note (1)

(1) All registers shown have asynchronous clear ports.

# Input/Output Clock Mode

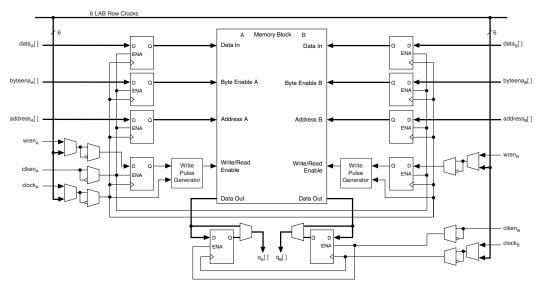

Input/output clock mode can be implemented for both the true and simple dual-port memory modes. On each of the two ports, A or B, one clock controls all registers for inputs into the memory block: data input, wren, and address. The other clock controls the block's data output registers. Each memory block port, A or B, also supports independent clock enables and asynchronous clear signals for input and output registers. Figures 2–18 and 2–19 show the memory block in input/output clock mode.

Figure 2–18. Input/Output Clock Mode in True Dual-Port Mode Note (1)

#### Note to Figure 2–18:

(1) All registers shown have asynchronous clear ports.

Figure 2–19. Input/Output Clock Mode in Simple Dual-Port Mode Note (1)

*Note to Figure 2–19:*(1) All registers shown except the rden register have asynchronous clear ports.

### **Read/Write Clock Mode**

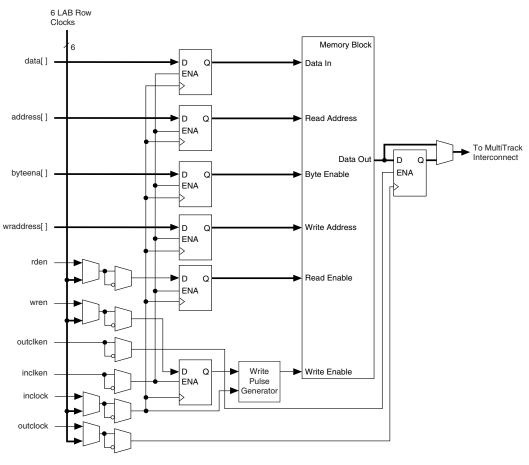

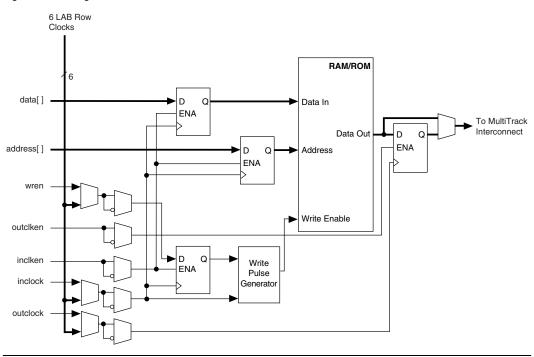

The M4K memory blocks implement read/write clock mode for simple dual-port memory. The designer can use up to two clocks in this mode. The write clock controls the block's data inputs, wraddress, and wren. The read clock controls the data output, rdaddress, and rden. The memory blocks support independent clock enables for each clock and asynchronous clear signals for the read- and write-side registers. Figure 2–20 shows a memory block in read/write clock mode.

Figure 2–20. Read/Write Clock Mode in Simple Dual-Port Mode Note (1)

*Note to Figure 2–20:*(1) All registers shown except the rden register have asynchronous clear ports.

### **Single-Port Mode**

The M4K memory blocks also support single-port mode, used when simultaneous reads and writes are not required. See Figure 2–21. A single M4K memory block can support up to two single-port mode RAM blocks if each RAM block is less than or equal to 2K bits in size.

### Figure 2–21. Single-Port Mode

# Global Clock Network & Phase-Locked Loops

Cyclone devices provide a global clock network and up to two PLLs for a complete clock management solution.

### **Global Clock Network**

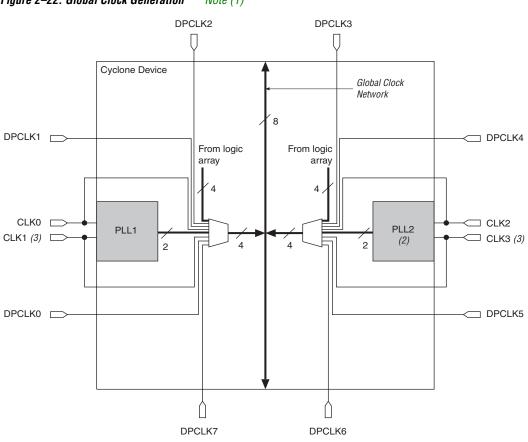

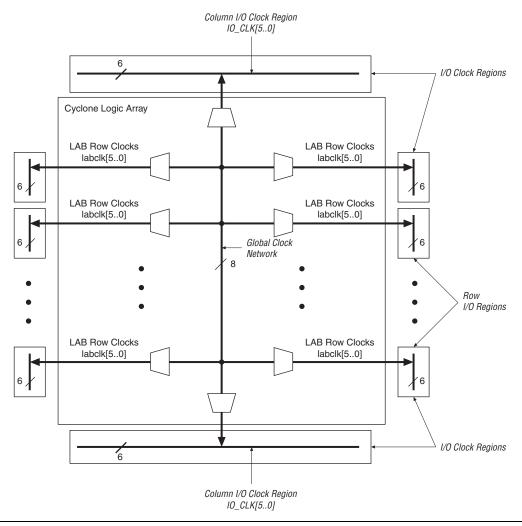

There are four dedicated clock pins (CLK[3..0], two pins on the left side and two pins on the right side) that drive the global clock network, as shown in Figure 2–22. PLL outputs, logic array, and dual-purpose clock (DPCLK[7..0]) pins can also drive the global clock network.

The eight global clock lines in the global clock network drive throughout the entire device. The global clock network can provide clocks for all resources within the device — IOEs, LEs, and memory blocks. The global clock lines can also be used for control signals, such as clock enables and synchronous or asynchronous clears fed from the external pin, or DQS signals for DDR SDRAM or FCRAM interfaces. Internal logic can also drive the global clock network for internally generated global clocks and asynchronous clears, clock enables, or other control signals with large fanout. Figure 2–22 shows the various sources that drive the global clock network.

Figure 2–22. Global Clock Generation Note (1)

Notes to Figure 2–22:

- The EPIC3 device in the 100-pin TQFP package has five DPCLK pins (DPCLK2, DPCLK3, DPCLK4, DPCLK6, and DPCLK7).

- (2) EP1C3 devices only contain one PLL (PLL 1).

- (3) The EP1C3 device in the 100-pin TQFP package does not have dedicated clock pins CLK1 and CLK3.

### **Dual-Purpose Clock Pins**

Each Cyclone device except the EP1C3 device has eight dual-purpose clock pins, DPCLK[7..0] (two on each I/O bank). EP1C3 devices have five DPCLK pins in the 100-pin TQFP package. These dual-purpose pins

can connect to the global clock network (see Figure 2–22) for high-fanout control signals such as clocks, asynchronous clears, presets, and clock enables, or protocol control signals such as TRDY and IRDY for PCI, or DQS signals for external memory interfaces.

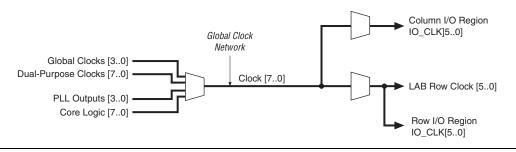

#### **Combined Resources**

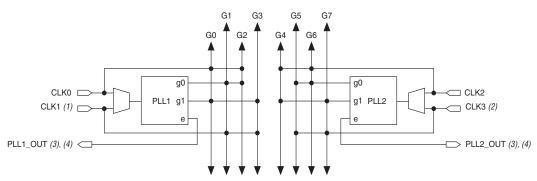

Each Cyclone device contains eight distinct dedicated clocking resources. The device uses multiplexers with these clocks to form six-bit buses to drive LAB row clocks, column IOE clocks, or row IOE clocks. See Figure 2–23. Another multiplexer at the LAB level selects two of the six LAB row clocks to feed the LE registers within the LAB.

IOE clocks have row and column block regions. Six of the eight global clock resources feed to these row and column regions. Figure 2–24 shows the I/O clock regions.

#### Figure 2–24. I/O Clock Regions

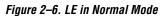

#### PLLs

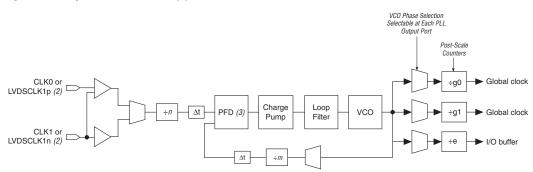

Cyclone PLLs provide general-purpose clocking with clock multiplication and phase shifting as well as outputs for differential I/O support. Cyclone devices contain two PLLs, except for the EP1C3 device, which contains one PLL. Table 2–6 shows the PLL features in Cyclone devices. Figure 2–25 shows a Cyclone PLL.

| Table 2–6. Cyclone PLL Features   |                                              |  |  |  |  |

|-----------------------------------|----------------------------------------------|--|--|--|--|

| Feature                           | PLL Support                                  |  |  |  |  |

| Clock multiplication and division | $m/(n \times \text{post-scale counter})$ (1) |  |  |  |  |

| Phase shift                       | Down to 125-ps increments (2), (3)           |  |  |  |  |

| Programmable duty cycle           | Yes                                          |  |  |  |  |

| Number of internal clock outputs  | 2                                            |  |  |  |  |

| Number of external clock outputs  | One differential or one single-ended (4)     |  |  |  |  |

#### Notes to Table 2-6:

- (1) The *m* counter ranges from 2 to 32. The *n* counter and the post-scale counters range from 1 to 32.

- (2) The smallest phase shift is determined by the voltage-controlled oscillator (VCO) period divided by 8.

- (3) For degree increments, Cyclone devices can shift all output frequencies in increments of 45°. Smaller degree increments are possible depending on the frequency and divide parameters.

- (4) The EP1C3 device in the 100-pin TQFP package does not support external clock output. The EP1C6 device in the 144-pin TQFP package does not support external clock output from PLL2.

Figure 2–25. Cyclone PLL Note (1)

#### Notes to Figure 2–25:

- The EP1C3 device in the 100-pin TQFP package does not support external outputs or LVDS inputs. The EP1C6 device in the 144-pin TQFP package does not support external output from PLL2.

- (2) LVDS input is supported via the secondary function of the dedicated clock pins. For PLL 1, the CLK0 pin's secondary function is LVDSCLK1p and the CLK1 pin's secondary function is LVDSCLK1n. For PLL 2, the CLK2 pin's secondary function is LVDSCLK2p and the CLK3 pin's secondary function is LVDSCLK2n.

- (3) PFD: phase frequency detector.

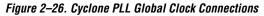

Figure 2–26 shows the PLL global clock connections.

#### Notes to Figure 2–26:

- (1) PLL 1 supports one single-ended or LVDS input via pins CLK0 and CLK1.

- (2) PLL2 supports one single-ended or LVDS input via pins CLK2 and CLK3.

- (3) PLL1\_OUT and PLL2\_OUT support single-ended or LVDS output. If external output is not required, these pins are available as regular user I/O pins.

- (4) The EP1C3 device in the 100-pin TQFP package does not support external clock output. The EP1C6 device in the 144-pin TQFP package does not support external clock output from PLL2.

Table 2–7 shows the global clock network sources available in Cyclone devices.

| Sou                 | irce        | GCLKO        | GCLK1 | GCLK2        | GCLK3        | GCLK4 | GCLK5        | GCLK6        | GCLK7        |

|---------------------|-------------|--------------|-------|--------------|--------------|-------|--------------|--------------|--------------|

| PLL Counter         | PLL1 G0     |              | ~     | ~            |              |       |              |              |              |

| Output              | PLL1 G1     | ~            |       |              | ~            |       |              |              |              |

|                     | PLL2 G0 (1) |              |       |              |              |       | $\checkmark$ | $\checkmark$ |              |

|                     | PLL2 G1 (1) |              |       |              |              | ~     |              |              | $\checkmark$ |

| Dedicated           | CLK0        | $\checkmark$ |       | $\checkmark$ |              |       |              |              |              |

| Clock Input<br>Pins | CLK1 (2)    |              | ~     |              | $\checkmark$ |       |              |              |              |

|                     | CLK2        |              |       |              |              | ~     |              | $\checkmark$ |              |

|                     | CLK3 (2)    |              |       |              |              |       | ~            |              | $\checkmark$ |

| Sou          | rce        | GCLKO        | GCLK1 | GCLK2 | GCLK3 | GCLK4 | GCLK5 | GCLK6        | GCLK7        |

|--------------|------------|--------------|-------|-------|-------|-------|-------|--------------|--------------|

| Dual-Purpose | DPCLK0 (3) |              |       |       | ~     |       |       |              |              |

| Clock Pins   | DPCLK1 (3) |              |       | ~     |       |       |       |              |              |

|              | DPCLK2     | $\checkmark$ |       |       |       |       |       |              |              |

|              | DPCLK3     |              |       |       |       | ~     |       |              |              |

|              | DPCLK4     |              |       |       |       |       |       | $\checkmark$ |              |

|              | DPCLK5 (3) |              |       |       |       |       |       |              | $\checkmark$ |

|              | DPCLK6     |              |       |       |       |       | ~     |              |              |

|              | DPCLK7     |              | ~     |       |       |       |       |              |              |

Notes to Table 2–7:

(1) EP1C3 devices only have one PLL (PLL 1).

(2) EP1C3 devices in the 100-pin TQFP package do not have dedicated clock pins CLK1 and CLK3.

(3) EP1C3 devices in the 100-pin TQFP package do not have the DPCLK0, DPCLK1, or DPCLK5 pins.

### **Clock Multiplication & Division**

Cyclone PLLs provide clock synthesis for PLL output ports using  $m/(n \times \text{post scale counter})$  scaling factors. The input clock is divided by a pre-scale divider, n, and is then multiplied by the m feedback factor. The control loop drives the VCO to match  $f_{\text{IN}} \times (m/n)$ . Each output port has a unique post-scale counter to divide down the high-frequency VCO. For multiple PLL outputs with different frequencies, the VCO is set to the least-common multiple of the output frequencies that meets its frequency specifications. Then, the post-scale dividers scale down the output frequencies required from one PLL are 33 and 66 MHz, the VCO is set to 330 MHz (the least-common multiple in the VCO's range).

Each PLL has one pre-scale divider, *n*, that can range in value from 1 to 32. Each PLL also has one multiply divider, *m*, that can range in value from 2 to 32. Global clock outputs have two post scale G dividers for global clock outputs, and external clock outputs have an E divider for external clock output, both ranging from 1 to 32. The Quartus II software automatically chooses the appropriate scaling factors according to the input frequency, multiplication, and division values entered.

### **External Clock Inputs**

Each PLL supports single-ended or differential inputs for sourcesynchronous receivers or for general-purpose use. The dedicated clock pins (CLK[3..0]) feed the PLL inputs. These dual-purpose pins can also act as LVDS input pins. See Figure 2–25.

Table 2–8 shows the I/O standards supported by PLL input and output pins.

| Table 2–8. PLL I/O Standards |              |               |  |  |  |  |

|------------------------------|--------------|---------------|--|--|--|--|

| I/O Standard                 | CLK Input    | EXTCLK Output |  |  |  |  |

| 3.3-V LVTTL/LVCMOS           | $\checkmark$ | $\checkmark$  |  |  |  |  |

| 2.5-V LVTTL/LVCMOS           | $\checkmark$ | $\checkmark$  |  |  |  |  |

| 1.8-V LVTTL/LVCMOS           | $\checkmark$ | ~             |  |  |  |  |

| 1.5-V LVCMOS                 | $\checkmark$ | $\checkmark$  |  |  |  |  |

| 3.3-V PCI                    | $\checkmark$ | $\checkmark$  |  |  |  |  |

| LVDS                         | $\checkmark$ | $\checkmark$  |  |  |  |  |

| SSTL-2 class I               | $\checkmark$ | ~             |  |  |  |  |

| SSTL-2 class II              | $\checkmark$ | ~             |  |  |  |  |

| SSTL-3 class I               | $\checkmark$ | $\checkmark$  |  |  |  |  |

| SSTL-3 class II              | $\checkmark$ | ~             |  |  |  |  |

| Differential SSTL-2          |              | $\checkmark$  |  |  |  |  |

For more information on LVDS I/O support, see "LVDS I/O Pins" on page 2–54.

## **External Clock Outputs**

Each PLL supports one differential or one single-ended output for sourcesynchronous transmitters or for general-purpose external clocks. If the PLL does not use these PLL\_OUT pins, the pins are available for use as general-purpose I/O pins. The PLL\_OUT pins support all I/O standards shown in Table 2–8.

The external clock outputs do not have their own V<sub>CC</sub> and ground voltage supplies. Therefore, to minimize jitter, do not place switching I/O pins next to these output pins. The EP1C3 device in the 100-pin TQFP package

does not have dedicated clock output pins. The EP1C6 device in the 144-pin TQFP package only supports dedicated clock outputs from PLL 1.

#### **Clock Feedback**

Cyclone PLLs have three modes for multiplication and/or phase shifting:

- Zero delay buffer mode—The external clock output pin is phasealigned with the clock input pin for zero delay.

- Normal mode—If the design uses an internal PLL clock output, the normal mode compensates for the internal clock delay from the input clock pin to the IOE registers. The external clock output pin is phase shifted with respect to the clock input pin if connected in this mode. The designer defines which internal clock output from the PLL should be phase-aligned to compensate for internal clock delay.

- No compensation mode—In this mode, the PLL will not compensate for any clock networks.

### **Phase Shifting**

Cyclone PLLs have an advanced clock shift capability that enables programmable phase shifts. Designers can enter a phase shift (in degrees or time units) for each PLL clock output port or for all outputs together in one shift. Designers can perform phase shifting in time units with a resolution range of 125 to 250 ps. The finest resolution equals one eighth of the VCO period. The VCO period is a function of the frequency input and the multiplication and division factors. Each clock output counter can choose a different phase of the VCO period from up to eight taps. Designers can use this clock output counter along with an initial setting on the post-scale counter to achieve a phase-shift range for the entire period of the output clock. The phase tap feedback to the m counter can shift all outputs to a single phase. The Quartus II software automatically sets the phase taps and counter settings according to the phase shift entered.

#### **Lock Detect Signal**

The lock output indicates that there is a stable clock output signal in phase with the reference clock. Without any additional circuitry, the lock signal may toggle as the PLL begins tracking the reference clock. Therefore, the designer may need to gate the lock signal for use as a system-control signal. For correct operation of the lock circuit below -20 C,  $f_{IN/N} > 200 \text{ MHz}$ .

### **Programmable Duty Cycle**

The programmable duty cycle allows PLLs to generate clock outputs with a variable duty cycle. This feature is supported on each PLL post-scale counter (g0, g1, e). The duty cycle setting is achieved by a low- and high-time count setting for the post-scale dividers. The Quartus II software uses the frequency input and the required multiply or divide rate to determine the duty cycle choices.

## **Control Signals**

There are three control signals for clearing and enabling PLLs and their outputs. The designer can use these signals to control PLL resynchronization and the ability to gate PLL output clocks for low-power applications.

The pllenable signal enables and disables PLLs. When the pllenable signal is low, the clock output ports are driven by ground and all the PLLs go out of lock. When the pllenable signal goes high again, the PLLs relock and resynchronize to the input clocks. An input pin or LE output can drive the pllenable signal.

The areset signals are reset/resynchronization inputs for each PLL. Cyclone devices can drive these input signals from input pins or from LEs. When areset is driven high, the PLL counters will reset, clearing the PLL output and placing the PLL out of lock. When driven low again, the PLL will resynchronize to its input as it relocks.

The pfdena signals control the phase frequency detector (PFD) output with a programmable gate. If you disable the PFD, the VCO will operate at its last set value of control voltage and frequency with some drift, and the system will continue running when the PLL goes out of lock or the input clock disables. By maintaining the last locked frequency, the system has time to store its current settings before shutting down. The designer can either use their own control signal or gated locked status signals to trigger the pfdena signal.

For more information on Cyclone PLLs, see *Chapter 6*, *Using PLLs in Cyclone Devices*.

## I/O Structure

IOEs support many features, including:

- Differential and single-ended I/O standards

- 3.3-V, 64- and 32-bit, 66- and 33-MHz PCI compliance

- Joint Test Action Group (JTAG) boundary-scan test (BST) support

- Output drive strength control

- Weak pull-up resistors during configuration

- Slew-rate control

- Tri-state buffers

- Bus-hold circuitry

- Programmable pull-up resistors in user mode

- Programmable input and output delays

- Open-drain outputs

- DQ and DQS I/O pins

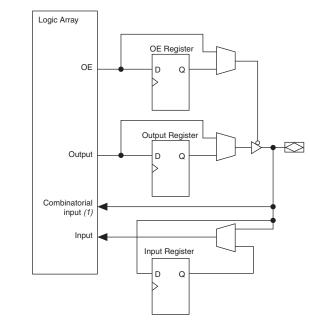

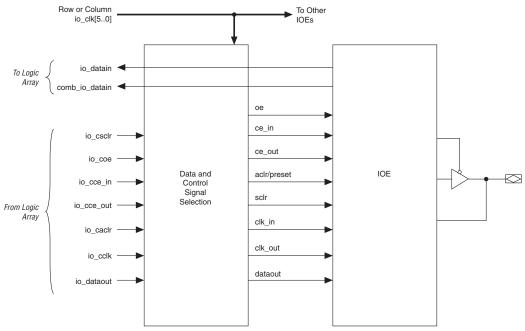

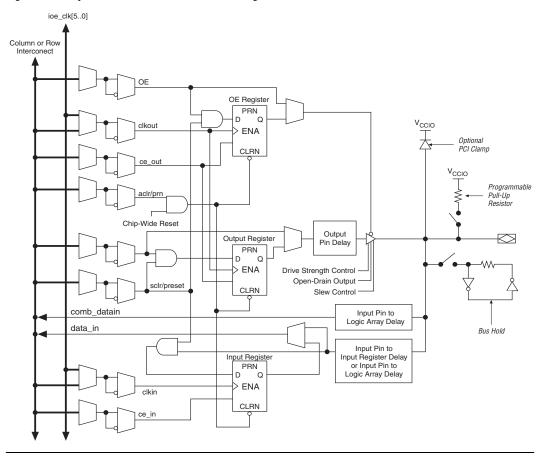

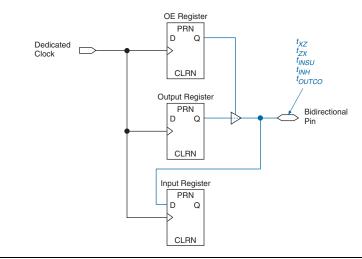

Cyclone device IOEs contain a bidirectional I/O buffer and three registers for complete embedded bidirectional single data rate transfer. Figure 2–27 shows the Cyclone IOE structure. The IOE contains one input register, one output register, and one output enable register. The designer can use the input registers for fast setup times and output registers for fast clock-to-output times. Additionally, the designer can use the output enable (OE) register for fast clock-to-output enable timing. The Quartus II software automatically duplicates a single OE register that controls multiple output or bidirectional pins. IOEs can be used as input, output, or bidirectional pins.

#### Note to Figure 2-27:

(1) There are two paths available for combinatorial inputs to the logic array. Each path contains a unique programmable delay chain.

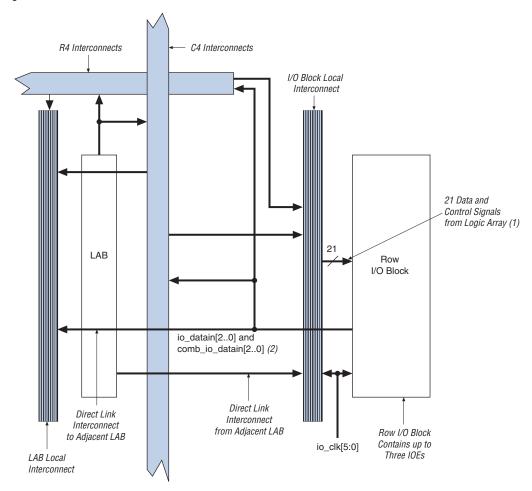

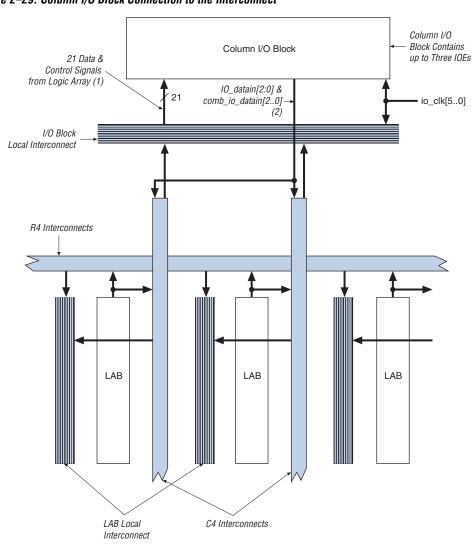

The IOEs are located in I/O blocks around the periphery of the Cyclone device. There are up to three IOEs per row I/O block and up to three IOEs per column I/O block (column I/O blocks span two columns). The row I/O blocks drive row, column, or direct link interconnects. The column I/O blocks drive column interconnects. Figure 2–28 shows how a row I/O block connects to the logic array. Figure 2–29 shows how a column I/O block connects to the logic array.

Figure 2–28. Row I/O Block Connection to the Interconnect

#### Notes to Figure 2–28:

- (1) The 21 data and control signals consist of three data out lines, io\_dataout[2..0], three output enables, io\_coe[2..0], three input clock enables, io\_cce\_in[2..0], three output clock enables, io\_cce\_out[2..0], three clocks, io\_cclk[2..0], three asynchronous clear signals, io\_caclr[2..0], and three synchronous clear signals, io\_csclr[2..0].

- (2) Each of the three IOEs in the row I/O block can have one io\_datain input (combinatorial or registered) and one comb\_io\_datain (combinatorial) input.

Figure 2–29. Column I/O Block Connection to the Interconnect

#### Notes to Figure 2–29:

- (1) The 21 data and control signals consist of three data out lines, io\_dataout[2..0], three output enables, io\_coe[2..0], three input clock enables, io\_cce\_in[2..0], three output clock enables, io\_cce\_out[2..0], three clocks, io\_cclk[2..0], three asynchronous clear signals, io\_caclr[2..0], and three synchronous clear signals, io\_csclr[2..0].

- (2) Each of the three IOEs in the column I/O block can have one io\_datain input (combinatorial or registered) and one comb\_io\_datain (combinatorial) input.

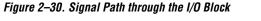

The pin's datain signals can drive the logic array. The logic array drives the control and data signals, providing a flexible routing resource. The row or column IOE clocks, io\_clk[5..0], provide a dedicated routing resource for low-skew, high-speed clocks. The global clock network generates the IOE clocks that feed the row or column I/O regions (see "Global Clock Network & Phase-Locked Loops" on page 2–29). Figure 2–30 illustrates the signal paths through the I/O block.

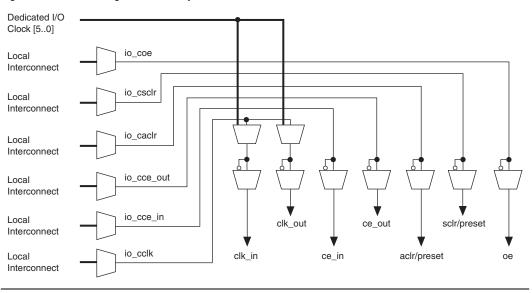

Each IOE contains its own control signal selection for the following control signals: oe, ce\_in, ce\_out, aclr/preset, sclr/preset, clk\_in, and clk\_out. Figure 2–31 illustrates the control signal selection.

Figure 2–31. Control Signal Selection per IOE

In normal bidirectional operation, the designer can use the input register for input data requiring fast setup times. The input register can have its own clock input and clock enable separate from the OE and output registers. The output register can be used for data requiring fast clock-tooutput performance. The OE register is available for fast clock-to-output enable timing. The OE and output register share the same clock source and the same clock enable source from the local interconnect in the associated LAB, dedicated I/O clocks, or the column and row interconnects. Figure 2–32 shows the IOE in bidirectional configuration.

Figure 2–32. Cyclone IOE in Bidirectional I/O Configuration

The Cyclone device IOE includes programmable delays to ensure zero hold times, minimize setup times, or increase clock to output times.

A path in which a pin directly drives a register may require a programmable delay to ensure zero hold time, whereas a path in which a pin drives a register through combinatorial logic may not require the delay. Programmable delays decrease input-pin-to-logic-array and IOE input register delays. The Quartus II Compiler can program these delays to automatically minimize setup time while providing a zero hold time. Programmable delays can increase the register-to-pin delays for output registers. Table 2–9 shows the programmable delays for Cyclone devices.

| Table 2–9. Cyclone Programmable Delay Chain |                                         |  |  |  |

|---------------------------------------------|-----------------------------------------|--|--|--|

| Programmable Delays Quartus II Logic Option |                                         |  |  |  |

| Input pin to logic array delay              | Decrease input delay to internal cells  |  |  |  |

| Input pin to input register delay           | Decrease input delay to input registers |  |  |  |

| Output pin delay                            | Increase delay to output pin            |  |  |  |

There are two paths in the IOE for a combinatorial input to reach the logic array. Each of the two paths can have a different delay. This allows the designer to adjust delays from the pin to internal LE registers that reside in two different areas of the device. The designer sets the two combinatorial input delays by selecting different delays for two different paths under the **Decrease input delay to internal cells** logic option in the Quartus II software. When the input signal requires two different delays for the combinatorial input, the input register in the IOE is no longer available.

The IOE registers in Cyclone devices share the same source for clear or preset. The designer can program preset or clear for each individual IOE. The designer can also program the registers to power up high or low after configuration is complete. If programmed to power up low, an asynchronous clear can control the registers. If programmed to power up high, an asynchronous preset can control the registers. This feature prevents the inadvertent activation of another device's active-low input upon power up. If one register in an IOE uses a preset or clear signal then all registers in the IOE must use that same signal if they require preset or clear. Additionally a synchronous reset signal is available to the designer for the IOE registers.

#### **External RAM Interfacing**

Cyclone devices support DDR SDRAM and FCRAM interfaces at up to 133 MHz through dedicated circuitry.

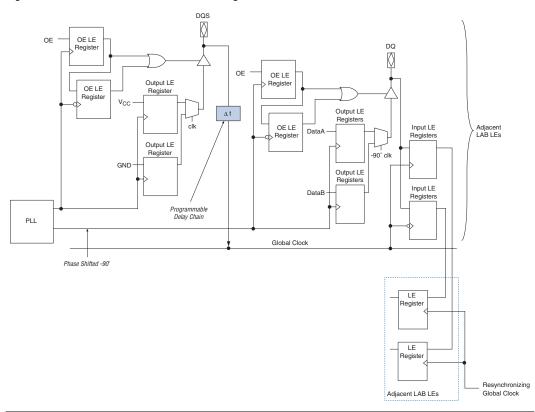

### **DDR SDRAM & FCRAM**

Cyclone devices have dedicated circuitry for interfacing with DDR SDRAM. All I/O banks support DDR SDRAM and FCRAM I/O pins. However, the configuration input pins in bank 1 must operate at 2.5 V because the SSTL-2  $V_{CCIO}$  level is 2.5 V. Additionally, the configuration

output pins (nSTATUS and CONF\_DONE) and all the JTAG pins in I/O bank 3 must operate at 2.5 V because the  $V_{CCIO}$  level of SSTL-2 is 2.5 V. I/O banks 1, 2, 3, and 4 support DQS signals with DQ bus modes of  $\times 8$ .

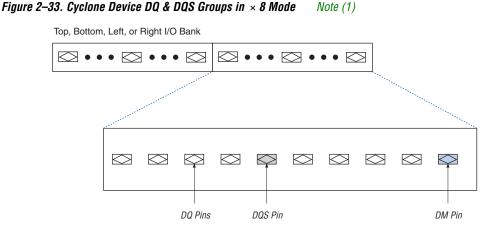

For × 8 mode, there are up to eight groups of programmable DQS and DQ pins, I/O banks 1, 2, 3, and 4 each have two groups in the 324-pin and 400-pin FineLine BGA packages. Each group consists of one DQS pin, a set of eight DQ pins, and one DM pin (see Figure 2–33). Each DQS pin drives the set of eight DQ pins within that group.

#### Note to Figure 2–33:

(1) Each DQ group consists of one DQS pin, eight DQ pins, and one DM pin.

Table 2–10 shows the number of DQ pin groups per device.

| Table 2–10. DQ Pin Groups (Part 1 of 2) |                      |                                |                       |  |  |  |  |

|-----------------------------------------|----------------------|--------------------------------|-----------------------|--|--|--|--|

| Device                                  | Package              | Number of × 8 DQ<br>Pin Groups | Total DQ Pin<br>Count |  |  |  |  |

| EP1C3                                   | 100-pin TQFP (1)     | 3                              | 24                    |  |  |  |  |

|                                         | 144-pin TQFP         | 4                              | 32                    |  |  |  |  |

| EP1C4                                   | 324-pin FineLine BGA | 8                              | 64                    |  |  |  |  |

|                                         | 400-pin FineLine BGA | 8                              | 64                    |  |  |  |  |

| Table 2–10. DQ Pin Groups (Part 2 of 2) |                      |                                |                       |  |  |  |  |

|-----------------------------------------|----------------------|--------------------------------|-----------------------|--|--|--|--|

| Device                                  | Package              | Number of × 8 DQ<br>Pin Groups | Total DQ Pin<br>Count |  |  |  |  |

| EP1C6                                   | 144-pin TQFP         | 4                              | 32                    |  |  |  |  |

|                                         | 240-pin PQFP         | 4                              | 32                    |  |  |  |  |

|                                         | 256-pin FineLine BGA | 4                              | 32                    |  |  |  |  |

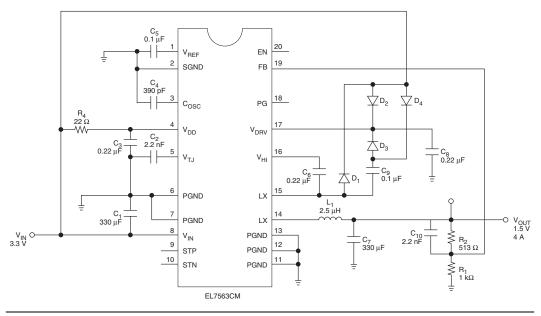

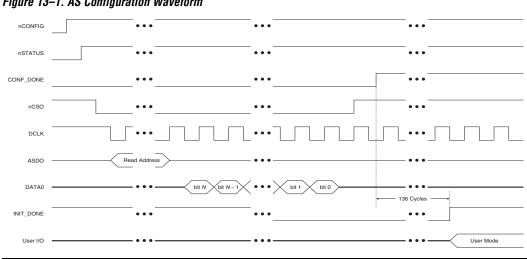

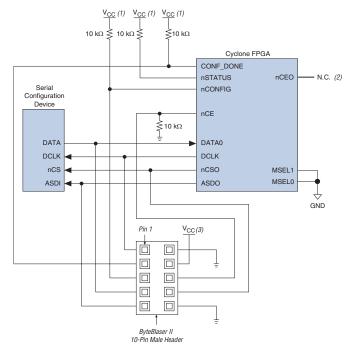

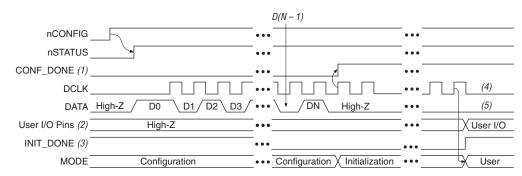

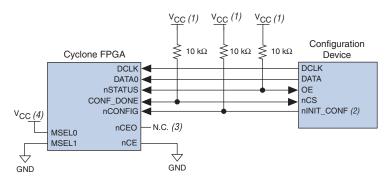

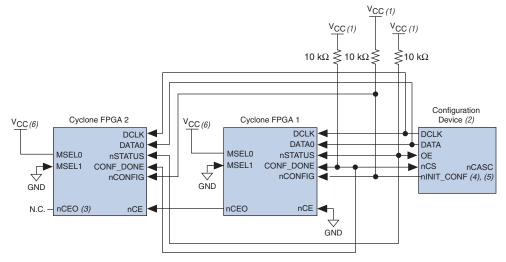

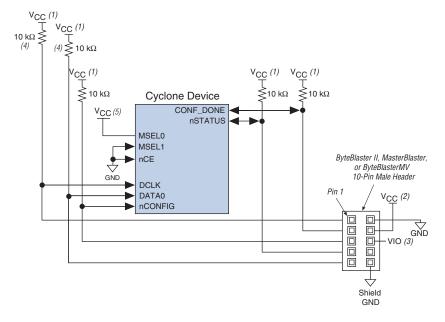

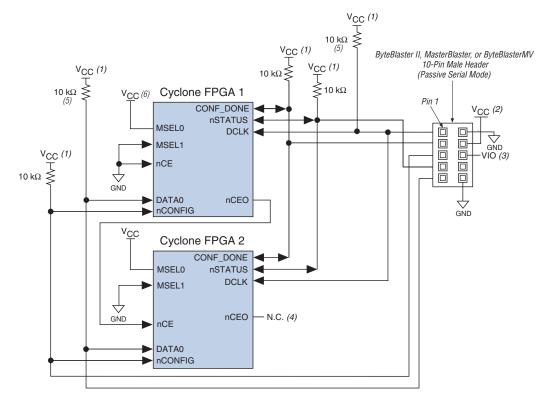

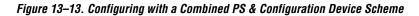

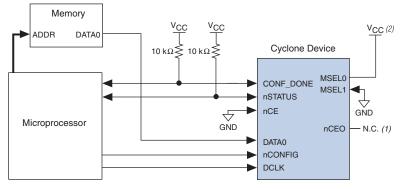

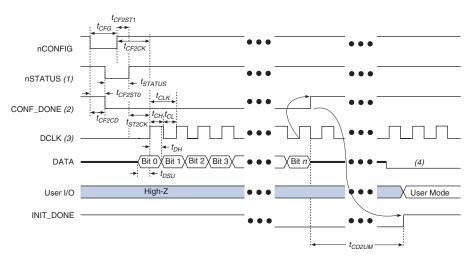

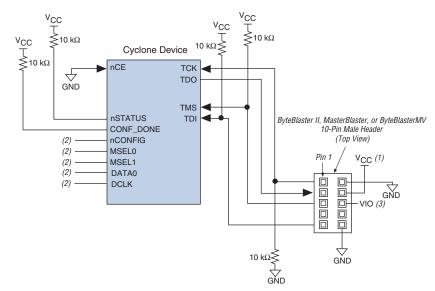

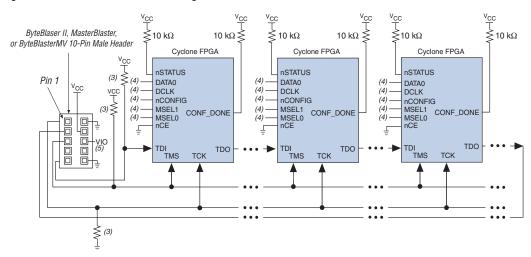

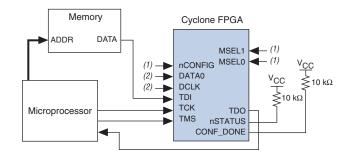

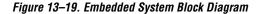

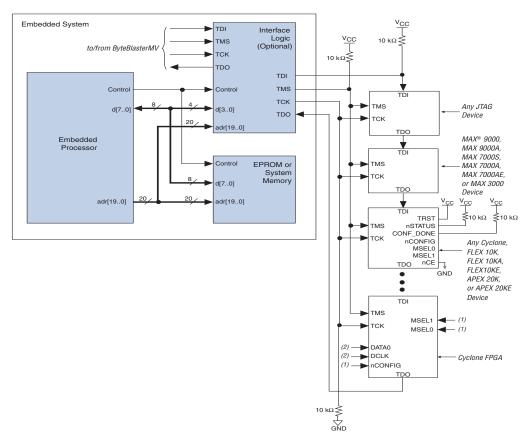

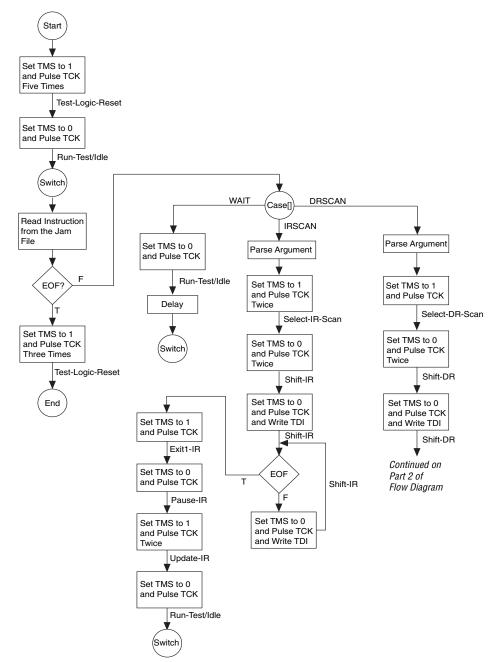

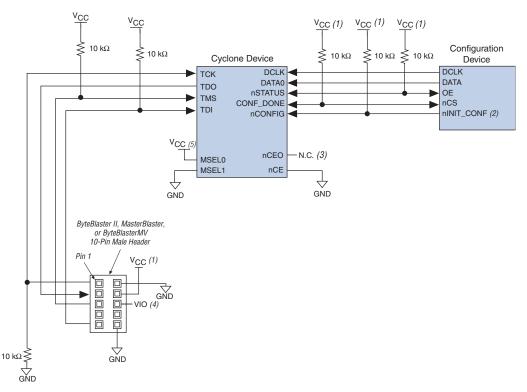

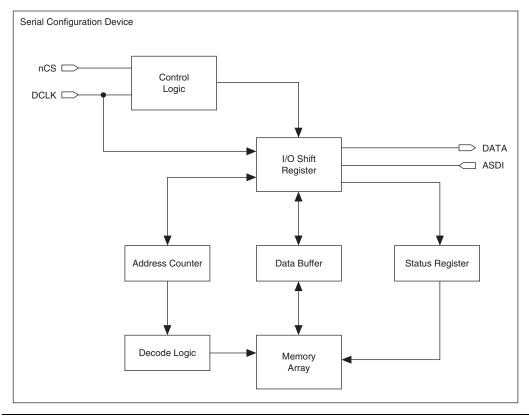

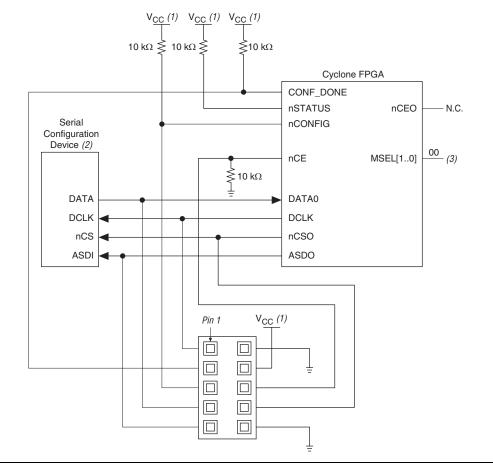

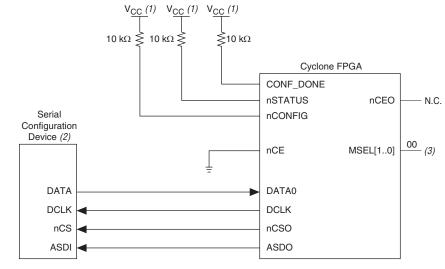

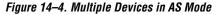

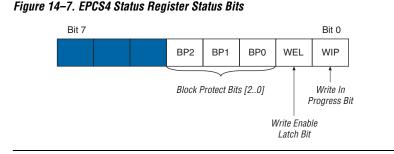

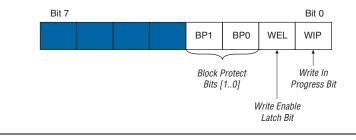

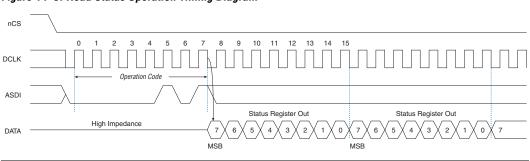

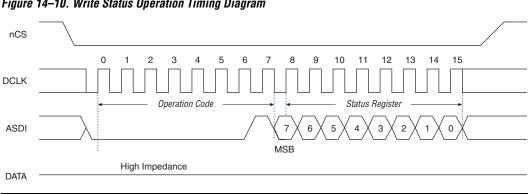

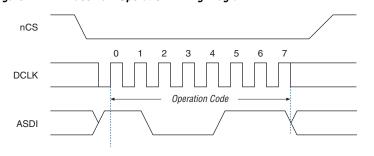

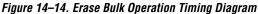

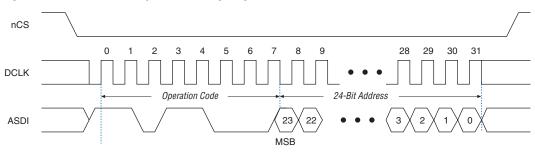

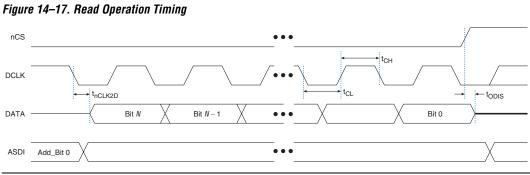

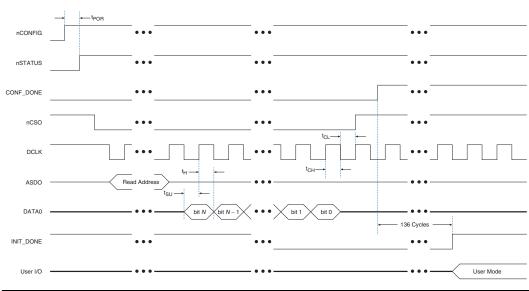

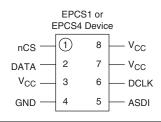

| EP1C12                                  | 240-pin PQFP         | 4                              | 32                    |  |  |  |  |